### INSTITUTO POLITÉCNICO NACIONAL

#### CENTRO DE INVESTIGACIÓN EN COMPUTACIÓN

# ANALIZADOR DE ESPECTRO UTILIZANDO UNA TARJETA PCI BASADA EN DSP'S

#### TESIS

QUE PARA OBTENER EL GRADO DE: MAESTRO EN CIENCIAS EN INGENIERÍA DE CÓMPUTO CON ESPECIALIDAD EN SISTEMAS DIGITALES

**PRESENTA**

### **JOSÉ MANUEL ROMERO XIMIL**

DIRECTOR: M. EN C. SERGIO SANDOVAL REYES

FEBRERO DEL 2002

A mis papás, Gregoria y Gerardo, y a mis hermanas, Natalia y Alejandra, por el apoyo incondicional que siempre me han dado y estar conmigo en todo momento.

A mis amigos, por su invaluable compañía.

A Gloria;)

#### **AGRADECIMIENTOS**

A mi director de tesis M. en C. Sergio Sandoval Reyes por su tiempo y buena disposición para asesorarme en la elaboración de esta tesis.

A todos los profesores de la Maestría en Ingeniería de Cómputo, en especial al Dr. Sergio Suárez Guerra con quien estuve trabajando en el desarrollo de un proyecto PIFI, en el que adquirí conocimientos útiles para la realización de la tesis y al M. en C. Osvaldo Espinosa Sosa por las enseñanzas en procesamiento digital de señales.

Al Centro de Investigación en Computación por permitirme cursar los estudios de maestría y utilizar la infraestructura necesaria para llevar a cabo el tema de tesis.

Al Instituto Politécnico Nacional, en el cual he cursado mis estudios de nivel medio superior, superior y maestría, por brindarme el apoyo económico para terminar mis estudios.

## ANALIZADOR DE ESPECTRO UTILIZANDO UNA TARJETA PCI BASADA EN DSP'S

José Manuel Romero Ximil

#### RESUMEN

El campo de la instrumentación virtual es cada vez más amplio, donde podemos emplear diversos instrumentos como voltímetros, osciloscopios, amperímetros, entre otros. Uno de estos instrumentos es el analizador de espectro, que muestra una señal en el dominio de la frecuencia, usado en muchos campos de la ciencia como la medicina, la acústica, la sismología, y otros. El desarrollo de un analizador de espectro utilizando una tarjeta PCI basada en DSP's es descrito en el presente trabajo. Dicha tarjeta realiza el análisis espectral de una señal eléctrica utilizando un convertidor ADC, una memoria, un DSP y una interfaz PCI, en combinación con los recursos de una computadora personal. La tarjeta se conecta al bus PCI de la computadora y a través de una interfaz gráfica despliega el espectro en la pantalla. La tarjeta PCI utiliza el convertidor de señal analógica a señal digital para obtener muestras de la señal eléctrica. El procesamiento de las muestras para obtener la estimación de la potencia del espectro de la señal, se realiza con la Transformada Rápida de Fourier (FFT) a través de un DSP y una memoria que se encuentran en la tarjeta. Los datos que contienen el espectro de la señal son almacenados temporalmente en dicha memoria y transferidos al CPU de la computadora con la ayuda de un controlador para el bus PCI. En la computadora se desarrolló un programa que se encarga de recibir los datos que contienen el espectro de la señal y los despliega en la pantalla de la computadora. De esta manera, se proporciona un instrumento de medición que utiliza los recursos de una computadora.

## SPECTRUM ANALYZER USING A DSP-BASED PCI BOARD

Jose Manuel Romero Ximil

#### **ABSTRACT**

As the virtual instrument field becomes broader, we can use many instruments such as voltmeters, oscilloscopes, ammeters, and others. One of these is the spectrum analyzer, which shows an input signal at frequency domain. It is used in many science fields like Medicine, Acoustics, Seismology, Speech Recognition and others. A spectrum analyzer using a DSP-based PCI board is described in this thesis. This one performs spectral analysis of an input signal using a board containing an ADC, memory, a DSP and a PCI interface that goes inside a PC. The board plugs into a computer PCI bus and through a graphic interface displays the spectrum on screen. The PCI board uses an ADC to get electric signal samples. Then the power spectrum estimation is obtained processing the samples through the Fast Fourier Transform (FFT) using the board's DSP and memory. Spectrum data are provisionally stored in memory and transferred to the CPU using a PCI bus controller. A spectrum analyzer program reads the spectrum data from PCI board and displays it on screen. In this way, a measurement instrument that uses PC resources is accomplished.

## ÍNDICE

| RESUMEN                                                                                                                                                                                                                                                                                                     | V                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                    | vi                                     |

| ÍNDICE                                                                                                                                                                                                                                                                                                      | vii                                    |

| LISTA DE FIGURAS Y TABLAS                                                                                                                                                                                                                                                                                   | ix                                     |

| INTRODUCCIÓN                                                                                                                                                                                                                                                                                                | 1                                      |

| 1 ANALIZADOR DE ESPECTRO BASADO EN PC  1.1 Antecedentes 1.2 Descripción del problema 1.3 Definición del problema 1.4 Objetivos 1.4.1 Objetivo general 1.4.2 Objetivos específicos 1.5 Justificación 1.6 Resumen                                                                                             | 3<br>4<br>5<br>5<br>5<br>5<br>5        |

| 2 ANALIZADORES DE ESPECTRO COMERCIALES Y SOLUCIÓN PROPUESTA 2.1 Soluciones afines 2.1.1 Solución National Instruments 2.1.2 Solución Hewlett Packard 2.2 Solución propuesta 2.3 Resumen                                                                                                                     | 6<br>6<br>8<br>9                       |

| 3 TARJETA QUE FUNCIONA COMO ANALIZADOR DE ESPECTRO 3.1 Descripción del funcionamiento 3.2 Hardware y software a desarrollar 3.2.1 Hardware de la tarjeta PCI 3.2.2 Software para obtener el espectro en frecuencia de una señal 3.3 Recursos de cómputo a emplear 3.4 Pruebas de funcionamiento 3.5 Resumen | 11<br>13<br>13<br>14<br>14<br>14<br>15 |

| 4 DISEÑO E IMPLEMENTACIÓN DE LA TARJETA PCI 4.1 Diseño del hardware de análisis de espectro 4.1 1 Etapa de digitalización de la señal de entrada                                                                                                                                                            | 16<br>16                               |

|                                                         | Contenido |

|---------------------------------------------------------|-----------|

| 4.1.2 Almacenamiento de muestras                        | 19        |

| 4.1.3 Procesador digital de señales                     | 20        |

| 4.1.3.1 Configuración del DSP en la tarjeta             | 23        |

| 4.1.4 Interfaz PCI                                      | 24        |

| 4.1.4.1 Operación del dispositivo PCI S5920             | 25        |

| 4.1.4.2 Funcionamiento de la interfaz PCI de la tarjeta | 27        |

| 4.2 Diseño de la lógica de control                      | 30        |

| 4.2.1 Ecuaciones de control                             | 30        |

| 4.2.2 Máquina de estados                                | 35        |

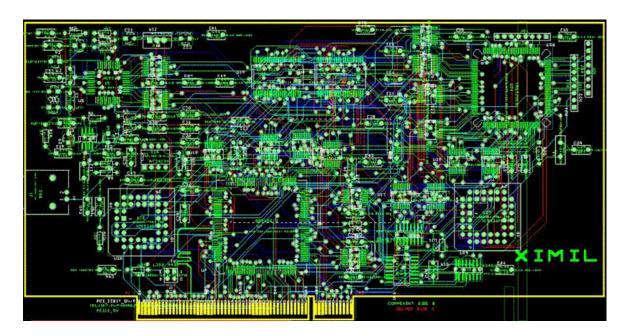

| 4.3 Implementación de la tarjeta                        | 38        |

| 4.4 Resumen                                             | 40        |

| 5 DISEÑO DEL SOFTWARE DE ANÁLISIS ESPECTRAL             | 41        |

| 5.1 Programa de procesamiento para el DSP               | 41        |

| 5.2 Controlador del dispositivo                         | 42        |

| 5.3 Presentación del espectro de la señal               | 45        |

| 5.4 Resumen                                             | 47        |

| 6 PRUEBAS Y RESULTADOS                                  | 48        |

| 6.1 Pruebas de la tarjeta para PC                       | 48        |

| 6.2 Resultados de mediciones                            | 50        |

| 6.3 Resumen                                             | 54        |

| 7 CONCLUSIONES                                          | 55        |

| 7.1 Logros alcanzados                                   | 55        |

| 7.2 Trabajos a futuro                                   | 56        |

| 7.3 Resumen                                             | 57        |

| BIBLIOGRAFÍA                                            | 58        |

| ANEXOS                                                  | 59        |

| A Diagrama eléctrico de la tarjeta PCI                  | 60        |

| B Operación del bus PCI                                 | 62        |

| C Registros de configuración PCI                        | 65        |

| D Programa de procesamiento para el DSP                 | 66        |

| F Programa que presenta el espectro en la computadora   | 78        |

#### LISTA DE FIGURAS Y TABLAS

### Figuras

| 1.1 | Espectro en frecuencia de una señal senoidal                            | 3  |

|-----|-------------------------------------------------------------------------|----|

| 2.1 | Tarjetas NI 4551 y NI 4552                                              | 7  |

|     | Diagrama de la tarjeta NI4551                                           | 8  |

|     | Analizador de señal dinámica de VirtualBench                            | 8  |

|     | Analizador de señal dinámica HP 35670A                                  | 9  |

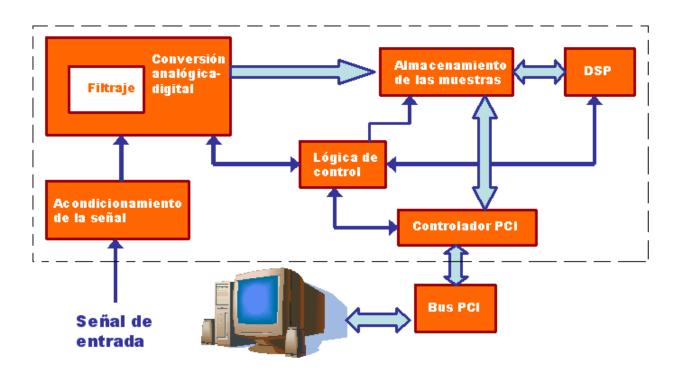

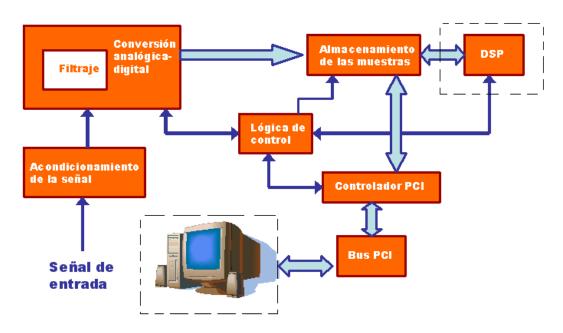

|     | Diagrama a bloques del analizador de espectro                           | 11 |

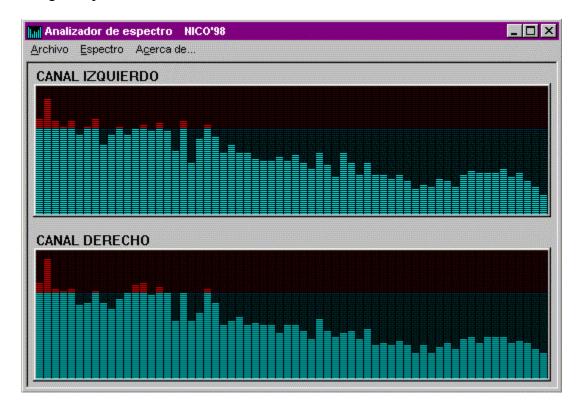

|     | Ventana que muestra una interfaz gráfica para un analizador de espectro | 13 |

| 4.1 | Diagrama a bloques de la tarjeta PCI                                    | 16 |

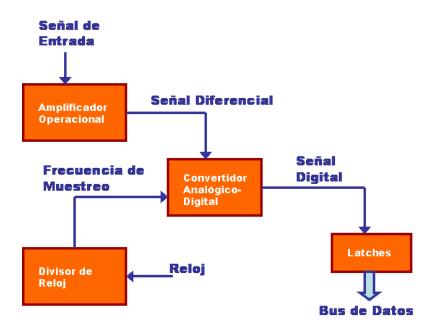

|     | Diagrama a bloques de la etapa de digitalización                        | 17 |

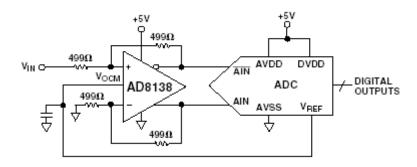

|     | Configuración típica del amplificador AD8138                            | 18 |

|     | Diagrama a bloques del convertidor AD9260                               | 18 |

|     | Bloques del almacenamiento de muestras                                  | 20 |

|     | Unidad central de procesamiento del C31                                 | 21 |

|     | Señales del TMS320C31                                                   | 23 |

|     | Diagrama a bloques del S5920                                            | 26 |

|     | Registros de configuración PCI en el S5920                              | 28 |

|     | Terminales del dispositivo S5920                                        | 29 |

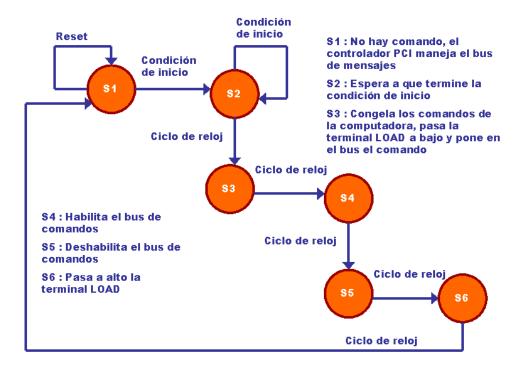

|     | Envío y recepción de comandos entre la tarjeta y la computadora         | 36 |

|     | Máquina de estados                                                      | 36 |

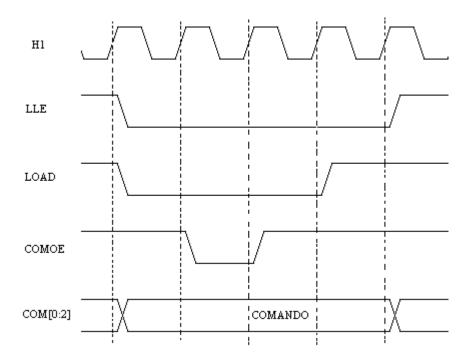

|     | Señales que genera la máquina de estados                                | 37 |

|     | Diseño del circuito impreso de la tarjeta PCI                           | 38 |

|     | Diseño del circuito impreso de la etapa de acondicionamiento            | 39 |

|     | Circuito impreso y componentes                                          | 39 |

|     | Bloques del software de análisis espectral                              | 41 |

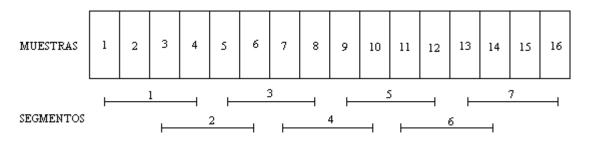

|     | División del conjunto de muestras en segmentos                          | 42 |

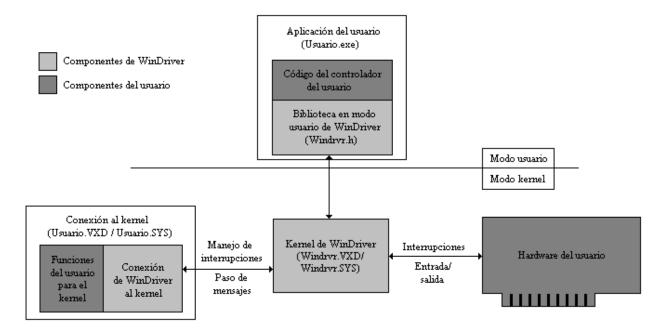

|     | Arquitectura de WinDriver                                               | 43 |

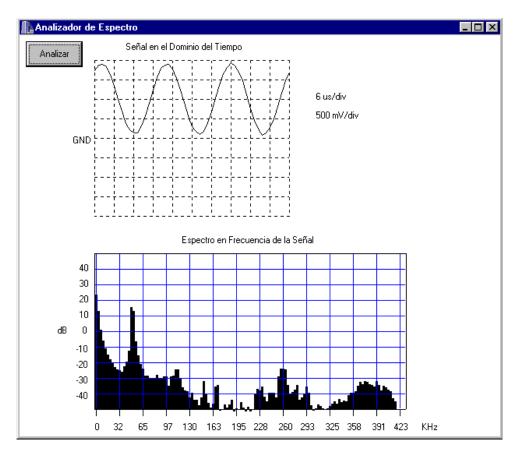

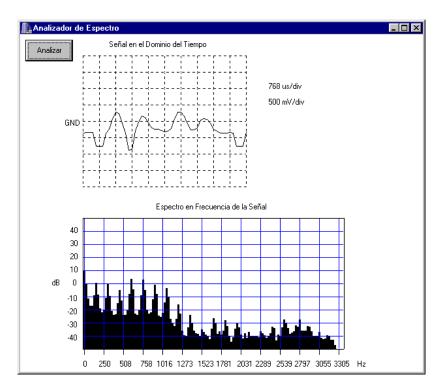

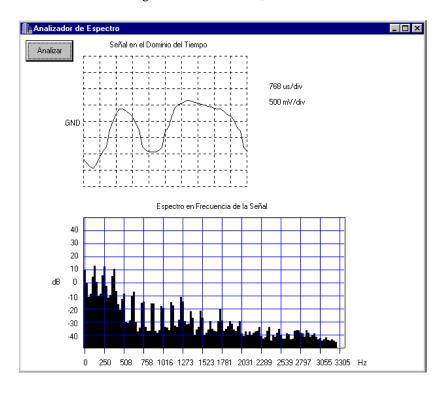

|     | Pantalla que muestra el software de análisis espectral                  | 47 |

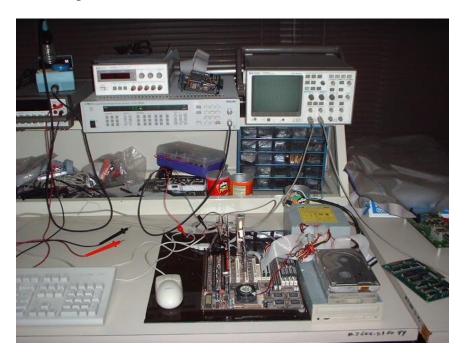

| 6.1 | Equipo de pruebas                                                       | 50 |

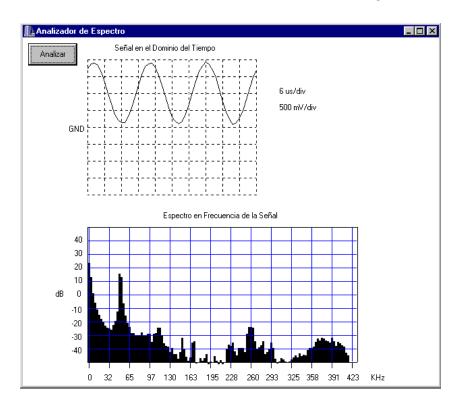

|     | Pantalla que muestra una señal de 50KHz en tiempo y frecuencia          | 51 |

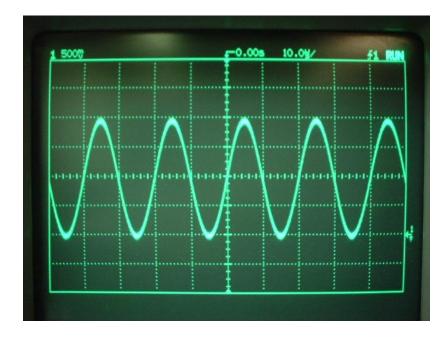

|     | Señal de 50KHz vista en el osciloscopio                                 | 51 |

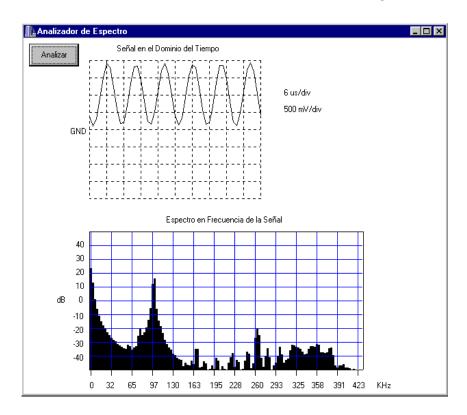

|     | Pantalla que muestra una señal de 100KHz en tiempo y frecuencia         | 52 |

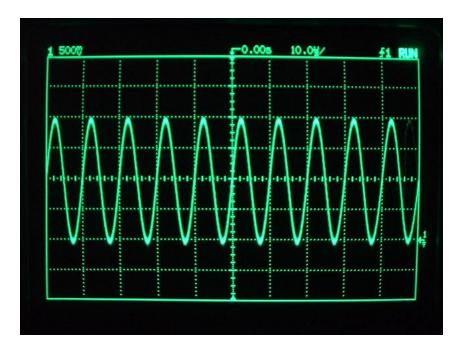

|     | Señal de 100KHz vista en el osciloscopio                                | 52 |

|     | Señal de voz, vocal A                                                   | 53 |

|     | Señal de voz, vocal E                                                   | 53 |

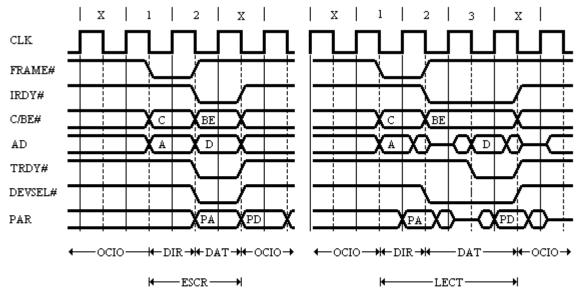

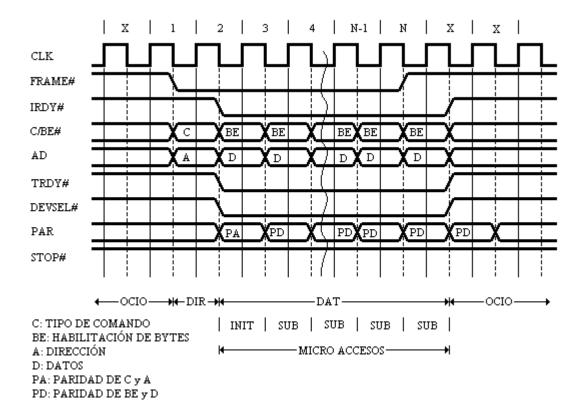

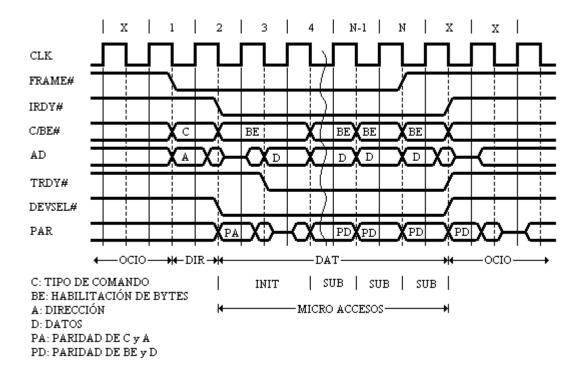

|     | Ciclos de acceso sencillo de escritura y de lectura del bus PCI         | 63 |

| B.2 | Ciclo de acceso de ráfaga de escritura del bus PCI                      | 64 |

| B 3 | Ciclo de acceso de ráfaga de lectura del bus PCI                        | 64 |

|                                                    | <u>Contenido</u> |

|----------------------------------------------------|------------------|

| Tablas                                             |                  |

| 4.1 Comandos que envía la computadora a la tarjeta | 30               |

| 4.2 Mensajes que envía la tarjeta a la computadora | 35               |

| 7.1 Especificaciones del analizador de espectro    | 56               |

| 7.2 Costo de la tarjeta                            | 56               |

| C.1 Registros de configuración PCI                 | 65               |

## **INTRODUCCIÓN**

La digitalización de señales es un área muy grande que se incluye en los campos del control, instrumentación y otros. La digitalización tiene muchas aplicaciones y las necesidades cada vez son mayores. Una de esas necesidades es la adquisición, almacenamiento y presentación de señales eléctricas en una computadora.

El procesamiento digital de señales hace posible desarrollar algunos instrumentos de medición que pueden interactuar con las computadoras, tal es el caso de los instrumentos basados en PC o instrumentos virtuales. Estos dispositivos toman ventaja de la capacidad de almacenamiento, procesamiento y presentación de éstas, reduciendo los costos y el tiempo de diseño. Aunque cabe destacar que también se limita el potencial de los mismos.

El siguiente trabajo propone el desarrollo de un analizador de espectro basado en una PC mediante una tarjeta PCI que utiliza un procesador de señales digitales. Con este fin hemos organizado la tesis en siete capítulos, los cuales se describen a continuación.

En el capítulo 1, **Analizador de espectro basado en PC**, se describe qué hace un analizador de espectro, así como la importancia que tiene en el desarrollo de proyectos de investigación y de aplicaciones. El desarrollo de instrumentos virtuales es una alternativa para las personas que no requieren un instrumento muy costoso y que además cuentan con una PC. Por esta razón se propone una tarjeta para computadora, que trabaja de manera conjunta con un programa de aplicación para funcionar como un analizador de espectro. Esta tarjeta se conecta al bus PCI de una PC y contiene un DSP que realiza el procesamiento de las señales. También se señalan los objetivos y se resalta la necesidad de contar con instrumentos en las áreas de diseño electrónico.

En el capítulo 2, **Analizadores de espectro comerciales y solución propuesta**, se mencionan algunas de las soluciones que existen en el mercado de los analizadores de espectro basados en PC. Entre estos productos se encuentran los fabricados por National Instruments y por Hewlett Packard, que son las compañías líderes tanto en instrumentos virtuales como en equipos de medición. También se menciona la solución propuesta, que consiste de una tarjeta PCI que utiliza un DSP para obtener el espectro en frecuencia de una señal muestreada, junto con un programa de aplicación que despliega el espectro en la pantalla de la computadora.

En el capítulo 3, **Tarjeta que funciona como analizador de espectro**, se describe el funcionamiento de un analizador de espectro, que consta básicamente de una etapa de acondicionamiento de la señal, una etapa de digitalización, una de almacenamiento de muestras, otra de procesamiento de los datos para encontrar el espectro en frecuencia de la señal y finalmente la transferencia del espectro a la computadora a través del bus PCI. El analizador de espectro consiste de una tarjeta con un DSP y un software que permite visualizar el espectro de la señal de entrada y controlar algunos recursos de la tarjeta.

En el capítulo 4, **Diseño e implementación de la tarjeta PCI**, se muestra el diseño de la tarjeta PCI basada en un DSP que va a ser utilizada como un analizador de espectro. Se describe cada uno de los bloques que conforman la tarjeta y qué función realizan en el procesamiento de la señal para obtener el espectro en frecuencia de la misma.

En el capítulo 5, **Diseño del software de análisis espectral**, se describe el desarrollo del programa que obtiene la estimación de la potencia del espectro de la señal, así como la interfaz de la tarjeta con el sistema operativo Windows, que presenta el espectro de la señal en la pantalla de la computadora.

En el capítulo 6, **Pruebas y resultados**, se mencionan las diferentes pruebas que se realizaron a la tarjeta para comprobar su funcionamiento adecuado y los resultados de las mediciones a un conjunto de señales eléctricas.

En el capítulo 7, **Conclusiones**, se describen los objetivos alcanzados en el desarrollo del trabajo y se proponen trabajos a futuro.

En la **Bibliografía** aparecen las fuentes consultadas para la elaboración de la tesis.

Finalmente, se integran el diagrama esquemático de la tarjeta, información del bus PCI y los archivos fuente de los programas en los **Anexos**.

## **CAPÍTULO 1**

## ANALIZADOR DE ESPECTRO BASADO EN PC

En el presente capítulo se describe la necesidad del uso de un analizador de espectro, un instrumento poco común en los laboratorios, debido a su elevado costo, pero que es fundamental en muchos campos de investigación aplicada.

#### 1.1 Antecedentes

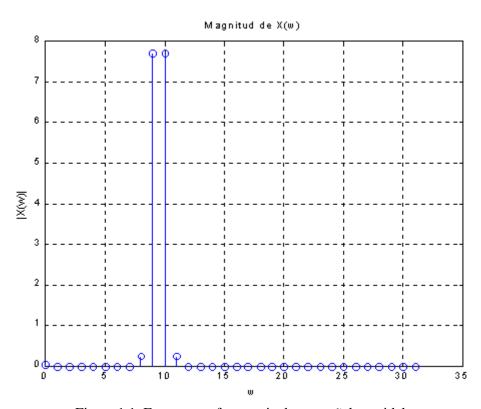

Figura 1.1. Espectro en frecuencia de una señal senoidal.

Un analizador de espectro [BG: 1988] puede ser pensado como un filtro con un ancho de banda estrecho que es barrido eléctricamente a través de un intervalo fijo de frecuencias mientras proporciona un despliegue visual de la amplitud de salida contra la frecuencia (figura 1.1).

El analizador de espectro nos permite observar una señal en el dominio de la frecuencia, es decir, podemos ver las magnitudes de las distintas frecuencias que conforman una señal dada.

El uso de los analizadores de espectro basados en PC no es muy común en México, algunas causas son el costo elevado de las unidades, se utilizan en casos muy particulares y son pocas las empresas que los venden.

Se han desarrollado varios proyectos que enfocan sus intereses a la construcción de instrumentos virtuales basados en una PC. La ventaja de los instrumentos virtuales radica en que se utiliza una infraestructura muy común en los centros de trabajo, las computadoras. Estos instrumentos son más económicos que los convencionales y por lo tanto son una buena opción para la gente que necesita un instrumento de medición y que cuenta con una computadora.

#### 1.2 Descripción del problema

El análisis de señales en el dominio de la frecuencia es de suma importancia en muchas áreas del conocimiento [ST: 1997]. En el monitoreo de vibración, el espectro de una señal muestreada nos da información sobre las características mecánicas de las partes bajo estudio. En el análisis de voz, nos ayuda al reconocimiento. En sistemas de radar y sonar, proporciona información sobre la localización de la fuente. En medicina, el análisis espectral de electrocardiogramas y electroencefalogramas proporciona material útil para diagnóstico. En sismología, puede ayudar a predecir los movimientos de la tierra. Aunque se observa que el uso del análisis espectral es muy útil en muchas áreas, no siempre se cuenta con un analizador de espectro, ya sea porque no existe en el centro de trabajo, o porque no está disponible para un gran número de personas. Y debe destacarse que aunque los analizadores de espectro se utilizan en muchas áreas, su uso es muy especializado.

Por esta razón, se propone un analizador de espectro basado en PC, que represente una opción para aquellos investigadores, estudiantes o profesionistas, que necesiten realizar análisis de señales en el dominio de la frecuencia.

Este instrumento consiste de una tarjeta que se conecta al bus PCI de una PC y de un software que permite interactuar al usuario con el hardware. La tarjeta se encarga de adquirir los datos, de procesarlos y de enviarlos, con la ayuda del software, a la computadora para su presentación en una pantalla. El tratamiento de los datos adquiridos lo realiza un procesador de señales digitales que, por medio de algoritmos matemáticos, encuentra el espectro en frecuencia de una señal dada.

El uso del bus PCI tiene muchas ventajas, como es la transferencia de datos de 32 bits a 33 MHz. Además, las computadoras actuales dan soporte a PCI más que a ningún otro tipo de bus y ya está quedando en desuso el estándar ISA, que se ha vuelto lento y poco efectivo en aplicaciones de tiempo real.

#### 1.3 Definición del problema

Construcción de un analizador de espectro de bajo costo que utiliza procesamiento digital de señales basado en una computadora personal con una interfaz PCI.

#### 1.4 Objetivos

#### 1.4.1 Objetivo general

Diseñar y construir una tarjeta PCI que utilice un procesador de señales digitales para que funcione como un analizador de espectro.

#### 1.4.2 Objetivos específicos

- Diseño y construcción de la tarjeta.

- Desarrollo del software de procesamiento para el DSP.

- Desarrollo de una interfaz gráfica para visualizar el espectro en una pantalla.

#### 1.5 Justificación

El desarrollo de una tarjeta para computadora que puede ser utilizada como un analizador de espectro, pondría al alcance de muchas personas la posibilidad de trabajar en sus proyectos, sin tener que recurrir a los pocos instrumentos de medición que se encuentran en los laboratorios o centros de trabajo, además de que se aprovecharían las características propias de las computadoras, como son su capacidad gráfica y de almacenamiento de datos y la posibilidad de compartir información con otras computadoras.

A pesar de que los instrumentos de este tipo ya se encuentran en el mercado, aún tienen un precio muy elevado, por encima del costo de una computadora personal. Entonces, el desarrollo de un instrumento a un precio más accesible, sería una buena alternativa para las personas que necesitan un analizador de espectro y que cuentan con una computadora personal.

#### 1.6 Resumen

En este capítulo se describió qué hace un analizador de espectro, así como la importancia que tiene en el desarrollo de proyectos de investigación y de aplicaciones. El desarrollo de instrumentos virtuales es una alternativa para las personas que no requieren un instrumento muy costoso y que además cuentan con una PC. Por esta razón se propone una tarjeta para computadora, que trabaja de manera conjunta con un programa de aplicación para funcionar como un analizador de espectro. Esta tarjeta se conecta al bus PCI de una PC y contiene un DSP que realiza el procesamiento de las señales. También se señalan los objetivos y se resalta la necesidad de contar con este instrumento en varias áreas del conocimiento. En el siguiente capítulo se menciona la solución que se hace al problema junto con una revisión de algunos analizadores de espectro que se encuentran en el mercado.

## **CAPÍTULO 2**

# ANALIZADORES DE ESPECTRO COMERCIALES Y SOLUCIÓN PROPUESTA

Existen en el mercado varias compañías que ofrecen productos de instrumentación virtual, entre las que destaca National Instruments (NI), además se encuentran aquellas compañías que venden instrumentos de medición convencionales, como Hewlett Packard (HP). A continuación se describen algunos productos de análisis de señales en el dominio de la frecuencia que ofrecen estas compañías y también se introduce la solución propuesta al problema planteado en el capítulo anterior.

#### 2.1 Soluciones afines

Existen varias compañías en el mercado que ofrecen instrumentos de medición, algunos son tarjetas que se insertan en la ranura de una computadora y las funciones que ofrecen son manipuladas por medio de software, otros son instrumentos que no dependen de una computadora, pero que pueden comunicarse con ella, facilitando ambos tipos el manejo de la información.

Sea de una forma u otra, en el caso de los analizadores de espectro, es utilizado cada vez más el procesamiento digital de señales como herramienta para desarrollar estos instrumentos. De esta manera vemos que compañías como HP y NI ofrecen algunos de sus productos basados en algoritmos matemáticos como la Transformada Rápida de Fourier (Fast Fourier Transform: FFT).

A continuación se describen algunos instrumentos de estas compañías.

#### 2.1.1 Solución National Instruments

NI fabrica tarjetas de adquisición de datos que se insertan en las ranuras de expansión de las computadoras. Entre estas tarjetas se encuentran aquellas que son especiales para utilizarse como instrumentos de adquisición de señal dinámica. Los modelos 4551 y 4552 [NI: 1998] son tarjetas PCI similares, que se utilizan como analizadores de señal dinámica (figura 2.1).

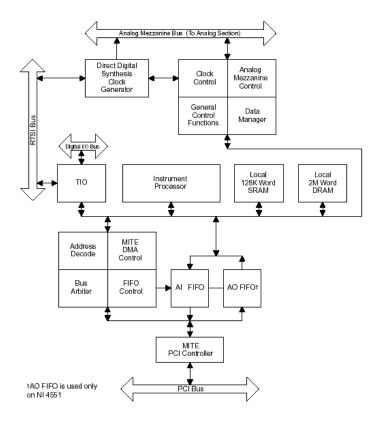

El NI 4551 tiene dos canales de entrada que hacen un muestreo simultáneo a una tasa de 204,800 muestras por segundo y dos canales de salida con actualizaciones simultáneas a una tasa de 51,200 muestras por segundo. Los convertidores, tanto de entrada como de salida, tienen una resolución de 16 bits y son del tipo delta-sigma. El NI 4552 tiene las mismas características que el NI 4551 en cuanto a sus componentes, pero tiene 4 canales de entrada y no tiene canales de salida. En la figura 2.2 se muestra el diagrama de la tarjeta.

Figura 2.1. Tarjetas NI 4551 y NI 4552.

Las aplicaciones que soporta son el procesamiento y análisis de señales de audio, investigación de acústica y voz, sonar, prueba y medición de frecuencias de audio, análisis de vibración, y cualquier aplicación que requiera alta fidelidad en la adquisición de señales con un ancho de banda de hasta 95 KHz.

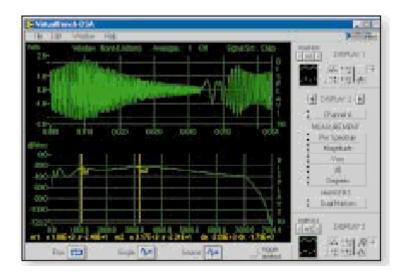

El software que acompaña a la tarjeta es el VirtualBench-DSA que permite utilizar la tarjeta como un analizador dinámico, para observar señales en el dominio de la frecuencia. También se puede utilizar toda una serie de productos de la misma compañía como LabVIEW, LabWindows, ComponentWorks, etc., estos programas son de propósito general y algunos tienen interfaces con lenguajes de programación como C.

El VirtualBench-DSA es una aplicación para el sistema operativo Windows que puede realizar varias funciones con la tarjeta NI 4551/4552 como medir distorsión armónica total, contenido armónico, respuesta en frecuencia, respuesta al impulso, espectro de potencia, espectro de amplitud, además de funciones de ventaneo. La ventana principal muestra una pantalla donde se puede visualizar la señal que se va a analizar y la señal después del análisis. Las distintas opciones y sus respectivos parámetros se introducen por medio de botones y cajas de diálogo (figura 2.3).

Figura 2.2. Diagrama de la tarjeta NI4551.

Figura 2.3. Analizador de señal dinámica de VirtualBench.

#### 2.1.2 Solución Hewlett Packard

HP se ha distinguido por la fabricación de instrumentos de medición, y entre sus productos se encuentra un analizador de señal dinámica, el HP 35670A [HP: 1997]. Es un equipo portátil que realiza análisis en el dominio de la frecuencia, del tiempo y de la amplitud (figura 2.4).

Los analizadores de espectro basados en la FFT, como el HP 35670A son ideales para la medición de espectro de señales de baja frecuencia como la voz o la vibración mecánica.

Este instrumento tiene dos canales de entrada, los canales comparten un ADC de 16 bits de resolución con un ancho de banda de 102,400 Hz.

Figura 2.4. Analizador de señal dinámica HP 35670A.

Este instrumento tiene una pantalla donde se puede visualizar el espectro de una señal, la señal misma (función en modo osciloscopio) y el análisis en el dominio de la amplitud. Tiene varios botones y perillas que controlan las funciones que se pueden utilizar y los parámetros que necesitan cada una de ellas. Además de ser portátil, puede almacenar las muestras en un disco de 3.5 pulgadas.

#### 2.2 Solución propuesta

Tomando como base las anteriores soluciones, la solución que se propone es una tarjeta PCI con funciones de un analizador de espectro. Esta tarjeta hace uso de la FFT para obtener el espectro en frecuencia de una señal muestreada. El algoritmo de la FFT es implementado en lenguaje ensamblador para el DSP TMS320C31 que es de la tercera generación de procesadores de señales digitales de Texas Instruments (TI). Este DSP puede realizar operaciones con números de punto flotante (reales). La tarjeta cuenta con un canal de entrada de 16 bits con una tasa máxima de dos y medio millones de muestras por segundo.

Los datos procesados en la tarjeta, por medio del DSP, se transfieren a la computadora, donde una aplicación para el sistema operativo Windows muestra el espectro de la señal. Esta aplicación puede manipular los parámetros necesarios para configurar el instrumento, como frecuencia de muestreo y número de muestras. Básicamente consiste de una pantalla que muestra las señales y un conjunto de botones y cajas de texto que permiten variar los parámetros.

Este analizador de espectro, a diferencia de los fabricados por HP y NI, utiliza un procesador de señales digitales de uso común, el TMS320C31 de TI. Esta compañía tiene mucho soporte para el desarrollo de aplicaciones y sus productos son un estándar en la industria. Además este instrumento está enfocado a aplicaciones que no necesiten el uso de varios canales de entrada. Esto permite que el costo de la tarjeta sea inferior en comparación a las otras soluciones. Algunas similitudes con las soluciones de HP y NI son que utiliza la FFT para realizar el análisis de señales, la vinculación con las computadoras personales, que es indispensable en los desarrollos de los últimos tiempos y el uso de un bus de alta velocidad como es el PCI, que es de gran utilidad para transferencias de bloques de datos.

#### 2.3 Resumen

En este capítulo se describieron algunas de las soluciones que existen en el mercado de los analizadores de espectro basados en PC. Entre estos productos se encuentran los fabricados por National Instruments y por Hewlett Packard, que son las compañías líderes tanto en instrumentos virtuales como en equipos de medición. También se menciona la solución propuesta, que consiste de una tarjeta PCI que utiliza un DSP para obtener el espectro en frecuencia de una señal muestreada, junto con un programa de aplicación que despliega el espectro en la pantalla de la computadora. En el siguiente capítulo se muestra una descripción funcional de la solución propuesta.

## **CAPÍTULO 3**

# TARJETA QUE FUNCIONA COMO ANALIZADOR DE ESPECTRO

En este capítulo se describe la forma como funciona un analizador de espectro basado en una PC y los bloques funcionales en que se divide. Además se menciona el hardware y el software que conforman al instrumento y el hardware y software necesario para el diseño.

#### 3.1 Descripción del funcionamiento

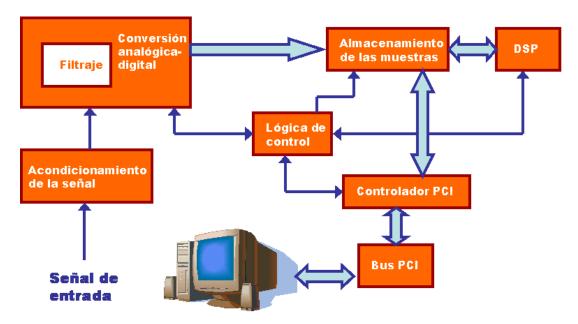

En la figura 3.1 se muestran los bloques que componen a un analizador de espectro basado en una PC con interfaz PCI. Primero, se necesita una etapa de acondicionamiento para manejar la señal que se desea digitalizar, esta etapa depende de las características de la etapa de conversión analógico-digital. Después, un ADC digitaliza la señal en forma de muestras que posteriormente se almacenan en memoria, para ser procesadas por el DSP en la siguiente etapa. Finalmente, los datos son transferidos a la computadora por medio de la interfaz PCI. Las muestras son transmitidas por el puerto PCI a la memoria del sistema en forma de bloque. La lógica de control permite manejar las distintas etapas.

Figura 3.1. Diagrama a bloques del analizador de espectro.

Cuando se desea observar el espectro de una señal en un analizador, se debe tomar en cuenta el voltaje máximo que acepta a la entrada el instrumento, el ancho de banda tanto de la señal como del instrumento, además de otras características. Para el caso de esta tarjeta PCI el voltaje máximo es de 4Vp-p. El ADC que utiliza la tarjeta requiere de un circuito que maneje la señal de entrada y que convierta la señal de entrada en una señal diferencial. Por esta razón se utiliza un circuito que convierte la señal referenciada a tierra a una señal diferencial y que puede manejar un ancho de banda suficiente para el ADC.

La etapa de conversión analógico-digital es la que se encarga de digitalizar la señal, asigna un número binario a un valor determinado de la amplitud de la señal, generando un conjunto de datos o muestras. Dentro de la etapa de digitalización se contempla un bloque de filtraje para eliminar componentes de frecuencia por encima del rango de entrada. El ADC debe proporcionar un ancho de banda amplio y una tasa de muestreo alta, ya que normalmente se desea observar señales que van desde unos cuantos hertz hasta más de 1 MHz. Normalmente los convertidores que se utilizan para este caso son del tipo delta-sigma, porque tienen buena resolución y su conversión es lineal.

El almacenamiento de los datos en la memoria es un punto muy importante, porque la velocidad en que la memoria puede guardar los datos, determina en cierta forma el rendimiento del sistema. Por eso, la memoria necesita ser de alta velocidad, para que pueda funcionar de manera conjunta con la interfaz PCI y lograr una alta tasa de transferencia de datos entre la tarjeta y la computadora. También es importante que esta memoria sea de fácil acceso para el DSP para que éste pueda realizar los cálculos de una forma más eficiente.

Un procesador de señales digitales realiza los cálculos necesarios para encontrar el espectro de la señal digitalizada. El DSP utiliza algoritmos matemáticos, entre los que se encuentra la FFT, para transportar la señal, del dominio del tiempo al dominio de la frecuencia. Estos procesadores están optimizados para realizar tareas en las que el uso exhaustivo de operaciones matemáticas es lo principal. Esta característica los hace ideales para esta aplicación.

La interfaz PCI es esencial en aplicaciones que requieren la transferencia de datos en tiempo real, en esta aplicación el uso de un bus de alta velocidad permite observar en la pantalla de la computadora el espectro de la señal de una forma más rápida y continua. El bus PCI es ya un estándar para las tarjetas que se insertan en una ranura de expansión de una PC, entonces su utilización en esta aplicación es necesaria.

La lógica de control se encarga de manipular los distintos dispositivos electrónicos, para asignar recursos, sincronizar la transferencia de datos y para decodificar comandos. Los dispositivos que realizan estas funciones necesitan ser de una velocidad que cumpla con los requerimientos de tiempo de los recursos de la tarjeta.

El espectro obtenido en la tarjeta se muestra en la pantalla de la computadora, pero también existe la posibilidad de observar la señal original, es decir, la tarjeta puede funcionar como un osciloscopio. La pantalla de la computadora simula el panel frontal de un instrumento convencional, es decir, se pueden observar perillas y botones, además de cajas de texto para introducir datos. Estos controles funcionarán de la misma manera que lo hacen sus contrapartes

en el otro tipo de instrumento, modifican los parámetros de digitalización y de esta forma controlan el hardware.

#### 3.2 Hardware y Software a desarrollar

El analizador de espectro consiste de una parte de hardware y otra de software. La parte de hardware la constituye la tarjeta PCI que utiliza un DSP para realizar los cálculos de la FFT. El software consiste de un programa de procesamiento para el DSP y de un programa de aplicación que muestra el espectro en frecuencia de la señal que se introduce en la tarjeta.

#### 3.2.1 Hardware de la tarjeta PCI

La tarjeta cuenta con un ADC delta-sigma para digitalizar la señal de entrada. Este ADC tiene incorporado un filtro que limita la frecuencia de la señal. Normalmente este tipo de convertidor es el que se utiliza para digitalizar señales en los analizadores de espectro. Las muestras son almacenadas en memoria mientras se digitaliza un número determinado de ellas. Posteriormente, las muestras son utilizadas en los cálculos que realiza el DSP TMS320C31 para encontrar el espectro de la señal. Cuando el DSP encuentra el espectro, los datos son enviados a la computadora, a través del bus PCI para que sean desplegados en la pantalla (un ejemplo de un espectro en frecuencia se muestra en la figura 3.2). La tarjeta cuenta con un circuito integrado que funciona como interfaz entre la tarjeta misma y el bus PCI en la computadora. Este circuito se hace cargo del protocolo de transferencia de datos.

Figura 3.2. Ventana que muestra una interfaz gráfica para un analizador de espectro.

#### 3.2.2 Software para obtener el espectro en frecuencia de una señal

El software que utiliza el analizador de espectro consiste de un programa para el DSP y otro para la computadora. El programa de procesamiento se ejecuta en el DSP, y obtiene la estimación de la potencia del espectro de una señal eléctrica. El programa de aplicación está formado por un manejador de dispositivo que permite el acceso al hardware de la tarjeta desde el sistema operativo Windows, para manipular algunas variables de la lógica de control y poder dar flexibilidad a la forma en que se van a muestrear las señales. Es importante el uso de una biblioteca de funciones que pueda tener acceso a los recursos del hardware, como es la suministrada por el programa WinDriver. Estas funciones ahorran una gran cantidad de tiempo en el desarrollo de manejadores de dispositivos. El programa de aplicación también consiste de una pantalla que representa el panel frontal de un instrumento convencional. Tiene un área para desplegar el espectro de la señal y cuenta con botones y cajas de texto para manipular los recursos de la tarjeta. El desarrollo del software involucra el uso de un entorno de programación visual como C++ Builder o Visual C++.

#### 3.3 Recursos de cómputo a emplear

- Computadora Pentium o superior con una ranura PCI disponible.

- Convertidor analógico-digital tipo delta-sigma de 16 bits.

- Chip controlador de bus PCI S5920.

- Memorias estáticas de alta velocidad.

- DSP TMS320C31 de Texas Instruments.

- Componentes de lógica programable.

- Programa WinDriver.

- C++ Builder para la programación de la aplicación.

- Kit de desarrollo TMS320C3X DSK.

#### 3.4 Pruebas de funcionamiento

Las pruebas que se deben realizar son las siguientes:

- Digitalización de la señal de entrada.

- Almacenamiento de las muestras en la memoria estática.

- Verificar que el algoritmo de la FFT funcione correctamente.

- Funcionamiento de la interfaz PCI para transferir y recibir datos entre la tarjeta y la computadora.

- Verificar que la lógica de control actualice las variables que se necesitan en la etapa de acondicionamiento y en la etapa de conversión.

- Comunicación de la tarjeta con el sistema operativo por medio del manejador.

- Verificar que el espectro mostrado en la pantalla sea el correcto, dado un conjunto de señales de entrada conocidas, como la función seno.

- Contrastar el espectro mostrado en la pantalla con el de otro instrumento, dada una misma señal de entrada.

#### 3.5 Resumen

En este capítulo se describió el funcionamiento de un analizador de espectro, que consta básicamente de una etapa de acondicionamiento de la señal, una etapa de digitalización, una de almacenamiento de muestras, otra de procesamiento de los datos para encontrar el espectro en frecuencia de la señal y finalmente la transferencia del espectro a la computadora a través del bus PCI. El analizador de espectro consiste de una tarjeta con un DSP y un software que permite visualizar el espectro de la señal de entrada y controlar algunos recursos de la tarjeta. En el siguiente capítulo se describe de forma detallada el funcionamiento de cada parte de la tarjeta.

# CAPÍTULO 4

## DISEÑO E IMPLEMENTACIÓN DE LA TARJETA PCI

En este capítulo se describe el funcionamiento de la tarjeta PCI que funciona como un analizador de espectro. Cada una de las partes que la componen se describe de forma detallada.

#### 4.1 Diseño del hardware de análisis de espectro

En esta sección se explica a detalle la configuración de los dispositivos que conforman la tarjeta PCI. El diagrama a bloques de la tarjeta se puede ver en la figura 4.1. Se resaltan los bloques que conforman la tarjeta, referente al hardware descrito en la sección 3.2.1.

Figura 4.1. Diagrama a bloques de la tarjeta PCI.

La señal de entrada pasa por una etapa de acondicionamiento, la cual produce una señal diferencial que es requerida por el ADC. Las muestras adquiridas por el ADC son almacenadas en memoria RAM. El DSP lee estas muestras y las procesa, aplicando, entre otras cosas, la FFT. Una vez que se ha procesado la señal en el DSP, se transfieren los datos almacenados en RAM hacia la computadora, por medio del bus PCI. Todos estos pasos son administrados por la lógica de control. Una vez que los datos procesados están en la computadora, el software de aplicación muestra el espectro de la señal. A continuación se describen más a detalle los bloques de acondicionamiento y de conversión.

#### 4.1.1 Etapa de digitalización de la señal de entrada

En la etapa de entrada de la señal se tiene por un lado un conector BNC por donde una señal es introducida, y por el otro lado se tiene un bus de 16 bits que transporta las muestras de la señal en dirección a la memoria RAM de la tarjeta. En la figura 4.2 se muestra un diagrama a bloques de esta parte de la tarjeta.

Figura 4.2. Diagrama a bloques de la etapa de digitalización.

Primero, la señal de entrada que es introducida por medio del conector BNC pasa por una etapa de acondicionamiento, conformada por el amplificador operacional AD8138 que convierte la señal referenciada a tierra en una señal diferencial, que va hacia el convertidor analógico/digital AD9260. La configuración del amplificador operacional se muestra en la figura 4.3. En esta figura se observa que tanto el convertidor como el amplificador operacional utilizan la misma alimentación de 5V y las terminales VOCM y VREF de los dispositivos se conectan entre sí para definir el voltaje de referencia de la señal, que es igual a 2.5V, la mitad del voltaje de alimentación.

Figura 4.3. Configuración típica del amplificador AD8138.

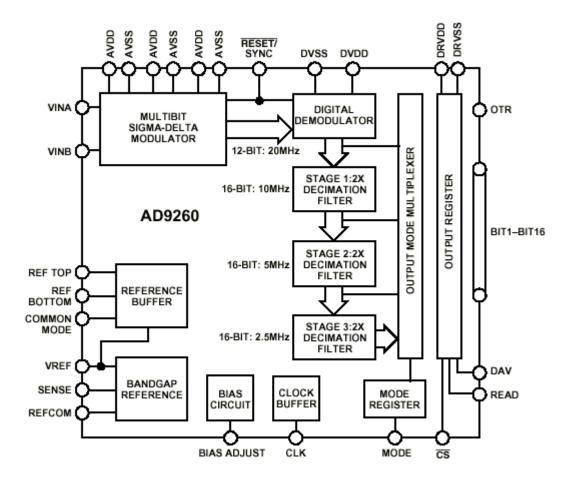

Se utiliza el convertidor analógico/digital AD9260 en la etapa de digitalización de la señal de entrada. El convertidor tiene una resolución de 16 bits y puede manejar una tasa de palabra de salida de 2.5MHz. En la figura 4.4 se muestra el diagrama a bloques del convertidor. Este convertidor puede trabajar sin un circuito de retención de señal porque hace un muestreo a una frecuencia de 20MHz. Además, cuenta con tres etapas de filtraje, que implementan tres filtros FIR pasabajos que se ajustan automáticamente a la frecuencia de muestreo y para una tasa de salida de 2.5MHz la frecuencia de corte es de 1.1MHz. De esta manera, se tiene todo un sistema de muestreo en un solo chip.

Figura 4.4. Diagrama a bloques del convertidor AD9260.

Se utiliza un circuito TC74VHC4040 para obtener, a partir de una frecuencia de 20MHz, un conjunto de frecuencias que sirven como reloj para el ADC. Este dispositivo es un contador de 12 bits y al ir incrementando su valor, se obtienen en sus terminales un conjunto de frecuencias menores a la introducida al reloj de este dispositivo. Para seleccionar una frecuencia específica de esas terminales, se utiliza un circuito multiplexor 74FCT151 que habilitar sólo una a la vez, este circuito utiliza tres bits de control que definen ocho diferentes frecuencias. Estos tres bits se pueden manipular por medio de software, escribiendo en los tres bits más significativos del byte 3 del buzón de salida PCI. Con estos dos circuitos, y con ayuda del software, podemos tener 8 diferentes tasas de muestreo para el convertidor.

El convertidor está configurado para que use una entrada diferencial de 4V pico a pico, esto se logra conectando sus terminales SENSE y REFCOM a tierra. El convertidor es capaz de operar en cuatro modos diferentes, proporcionando varias tasas de salida de datos. Colocando la terminal MODE en tierra se obtiene el mejor desempeño del dispositivo, proporcionando 2.5 millones de muestras por segundo. Para más detalles observar el diagrama en el Anexo A y ver la hoja de especificaciones del dispositivo.

Las terminales READ, OTR, DAV, /CS y /RESET del convertidor se utilizan para controlar la parte digital. READ y /CS controlan la salida de las muestras, estas terminales siempre están habilitadas, así, la información en los latches (que se observan en la figura 4.2) siempre está actualizada. OTR es la señal que indica un desbordamiento, la tarjeta no toma en cuenta los desbordamientos, por lo que no es utilizada esta terminal. DAV indica cuando hay una muestra disponible en la salida, esta señal se conecta a la lógica de control implementada en los CPLD's; y /RESET sirve para inicializar el convertidor, también se conecta a la lógica de control.

Finalmente, a la salida de los datos (en las terminales BIT1-16) se tienen latches que sirven como interfaz con el bus de datos de la tarjeta, que conecta al ADC con la memoria RAM en el bloque de almacenamiento de muestras. La lógica de control los habilita e inhabilita con la señal ADCOE.

#### 4.1.2 Almacenamiento de muestras

Para almacenar las muestras que proporciona el convertidor analógico-digital se utilizan dos memorias IDT71016 que tienen un bus de datos de 16 bits cada una y un bus de direcciones de 16 bits también. Una memoria representa los 16 bits menos significativos de la palabra de 32 bits y la otra representa los 16 bits más significativos.

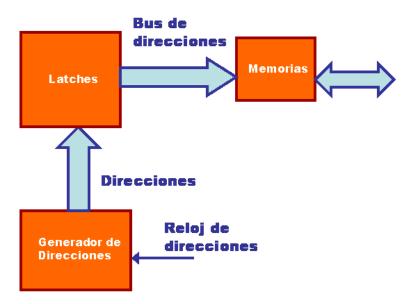

Puesto que el controlador PCI utiliza ciclos de acceso de ráfaga para realizar las transacciones de lectura y escritura, se requiere un circuito que genere las direcciones. El ADC tampoco genera direcciones. Por esta razón un circuito TC74VHC4040 se encarga de generar los 12 bits menos significativos del bus de direcciones para utilizarse con el controlador PCI y el ADC. Los cuatro bits restantes son generados por la lógica de control, para un total de 16 bits en el bus de direcciones. El reset, el reloj y la habilitación de la salida de este dispositivo son controlados por la lógica programada en los CPLDs. La figura 4.5 muestra los bloques que comprenden el almacenamiento de las muestras.

Figura 4.5. Bloques del almacenamiento de muestras.

Una vez que se tienen las muestras en la memoria RAM, el DSP comienza a procesar esos datos y el resultado del procesamiento lo guarda también en memoria RAM. La siguiente sección muestra las características del DSP y su importancia en el procesamiento de la señal.

#### 4.1.3 Procesador Digital de Señales

El dispositivo que se utiliza para realizar el procesamiento digital de las señales, en este caso la Transformada Rápida de Fourier, es el DSP TMS320C31 de la compañía Texas Instruments. A continuación se presenta una breve descripción del dispositivo [TI: 1997].

La arquitectura del DSP C31 responde a la demanda de sistemas basados en algoritmos aritméticos que requieren soluciones tanto de hardware como de software. Se obtiene un alto rendimiento por medio de la unidad de punto flotante, la memoria interna del dispositivo, el alto grado de paralelismo y el controlador de DMA. Estas características hacen al C31 una valiosa herramienta en el análisis del espectro de una señal.

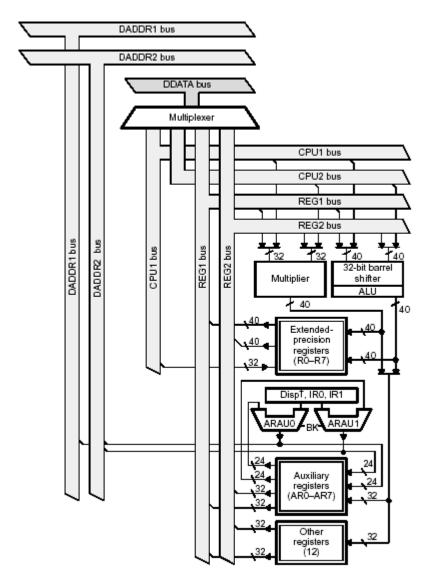

El C31 tiene una arquitectura de CPU basada en registros. La unidad central de procesamiento consiste de los componentes siguientes (ver figura 4.6):

- Multiplicador de punto flotante/enteros.

- Unidad aritmética lógica (ALU).

- Registro de corrimiento de 32 bits.

- Buses internos (CPU1/CPU2 y REG1/REG2).

- Unidades auxiliares de registros aritméticos (ARAUs).

- Otros registros.

El multiplicador realiza multiplicaciones de enteros de 24 bits y valores de punto flotante de 32 bits. La ALU ejecuta operaciones en un solo ciclo, de datos enteros de 24 bits, lógicos de 32 bits

y de punto flotante de 40 bits, incluyendo conversiones de enteros y de punto flotante. El registro de corrimiento es utilizado para desplazar hasta 32 bits hacia la izquierda o la derecha en un solo ciclo. Cuatro buses internos, CPU1, CPU2, REG1 y REG2 traen dos operandos de la memoria y dos operandos del archivo de registro, permitiendo multiplicaciones y sumas/restas en paralelo sobre cuatro operandos enteros o de punto flotante en un ciclo. Dos unidades auxiliares de registros aritméticos (ARAU0 y ARAU1) pueden generar dos direcciones en un ciclo. Las ARAUs operan en paralelo con el multiplicador y la ALU.

Figura 4.6. Unidad central de procesamiento del C31.

Los registros de precisión extendida (R7-R0) pueden almacenar y soportar operaciones de enteros de 24 bits y números de punto flotante de 32 bits. Los registros auxiliares de 32 bits (AR7-AR0) son accedidos por la CPU y modificados por las dos ARAUs. La función principal de los registros auxiliares es la generación de direcciones de 24 bits, también pueden ser usados como contadores o registros de propósito general de 32 bits que pueden ser modificados por el multiplicador y la ALU. El apuntador a la página de datos (DP) es un registro de 32 bits, los 8

bits menos significativos de este registro son utilizados por el modo de direccionamiento directo. Los registros índices de 32 bits (IR0 e IR1) contienen el valor usado por la ARAU para generar una dirección indexada. El apuntador a la pila del sistema (SP) es un registro de 32 bits que contiene la dirección del tope de la pila del sistema. El registro de estado (ST) contiene información global relacionada con el estado de la CPU. El registro de banderas de interrupción de la CPU (IF) también es de 32 bits. El registro de banderas de entrada/salida (IOF) controla el funcionamiento de las terminales externas XF0 y XF1. El contador de repeticiones (RC) es un registro de 32 bits que especifica el número de veces que se repite un bloque de código cuando se realiza una repetición de bloque. Cuando el procesador está operando en modo de repetición, el registro dirección de inicio de repetición (RS) de 32 bits contiene la dirección de inicio del bloque de memoria de programa a repetirse, y el registro dirección final de repetición (RE) de 32 bits contiene la dirección final del bloque a repetir.

El contador de programa (PC) es un registro de 32 bits que contiene la dirección de la siguiente instrucción a ser buscada. Aunque el contador de programa no es parte del archivo de registro de la CPU, es un registro que puede ser modificado por las instrucciones que modifican el flujo del programa.

El algoritmo de la FFT utiliza esencialmente operaciones aritméticas como multiplicaciones y sumas (ver capítulo 5 para más detalles), por esta razón, la arquitectura que se ha descrito es muy adecuada para este propósito. El programa que implementa el algoritmo es cargado en la memoria interna del DSP, con esto se logra un alto rendimiento, debido a la misma arquitectura. A continuación se explica el funcionamiento de la memoria interna del DSP, que se utiliza casi exclusivamente para almacenar el programa que implementa la FFT.

El espacio de memoria total del C31 es de 16 millones de palabras de 32 bits. El espacio de programa, datos y entrada/salida está contenido dentro de este espacio de direcciones de 16 millones de palabras, permitiendo el almacenamiento de tablas, coeficientes, código de programa, o datos. El C31 proporciona 2K X 32 bits de memoria interna, además de un cargador de arranque que permite cargar programa y datos al momento del reset por medio de memorias de 8, 16 ó 32 bits o por el puerto serial. Los buses separados de programa y datos permiten realizar operaciones de lectura/escritura en paralelo. Un caché de instrucciones de 64 X 32 bits es proporcionado para almacenar secciones de código que se repiten frecuentemente, lo cual reduce en gran medida el número de accesos fuera del chip.

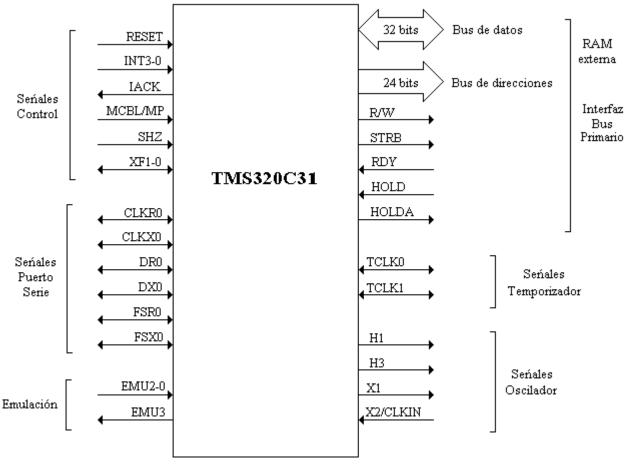

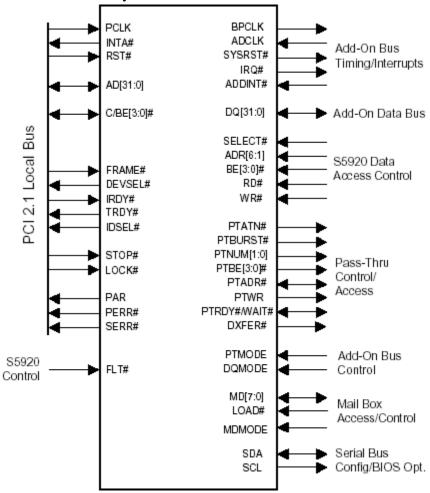

El C31 proporciona una interfaz externa: el bus primario (figura 4.7) [TI: 1999]. Esta interfaz consiste de un bus de datos de 32 bits, un bus de direcciones de 24 bits y un conjunto de señales de control. Direcciona memoria de programa/datos externa o espacio de entrada/salida. La tarjeta PCI la utiliza para acceder a los datos que se encuentran en la memoria RAM.

El DSP soporta 4 interrupciones externas (INT3 – INT0), un número de interrupciones internas y una señal de reset externa no mascarable. Estas interrupciones se utilizan también para configurar el cargador de arranque. La tarjeta PCI utiliza la interrupción 1 para cargar el programa en la memoria interna del DSP.

Dos banderas externas de entrada/salida, XF0 y XF1, pueden ser configuradas como terminales de entrada o salida bajo el control del software. La bandera XF0 es utilizada para señalar al DSP que debe iniciar el procesamiento de la señal.

Figura 4.7. Señales del TMS320C31.

Para mayor información consultar el manual de usuario del DSP TMS320C3X que se puede obtener en la página de Internet de Texas Instruments www.ti.com.

#### 4.1.3.1 Configuración del DSP en la tarjeta

El DSP TMS320C31 utiliza un bus de datos de 32 bits y un bus de direcciones de 24 bits. Para evitar problemas de colisiones en los buses de la tarjeta que llegan a la memoria RAM, las terminales del bus de datos del C31 se conectan a dispositivos FCT245 que controlan el acceso al bus de datos de la tarjeta y las terminales del bus de direcciones del C31 se conectan a dispositivos FCT573 que controlan el acceso al bus de direcciones de la tarjeta. La terminal R/W controla la dirección de los datos en los dispositivos FCT245. Los ocho bits más significativos del bus de direcciones A24-A31 se conectan a un CPLD para utilizar las señales en la lógica de control.

El C31 puede ser configurado para que trabaje en modo microprocesador o en modo microcomputadora, en este sentido se ha conectado la terminal MCBL/MP a VCC para que

trabaje en modo microcomputadora, que hace uso del cargador de arranque para cargar un programa desde un dispositivo externo, en este caso, la memoria RAM de la tarjeta.

La terminal RDY se conecta a tierra para indicar que no se van a introducir estados de espera por hardware. La terminal HOLD se usa para bloquear al C31, en la tarjeta, esta terminal se conecta a VCC para que el dispositivo no quede bloqueado y la terminal HOLDA queda desconectada, pues indica cuando se ha bloqueado el sistema. La terminal SHZ se conecta a VCC para que las terminales del DSP siempre estén habilitadas, esta terminal en estado bajo pone todas las señales del DSP en alta impedancia. Las terminales INT1 y RESET son controladas por la lógica programada en los CPLD's para cargar un programa en la memoria interna del DSP. Las terminales INT0, INT2 e INT3 son conectadas a VCC para evitar que se produzca una interrupción por medio de ellas. La terminal XF0 es controlada por un CPLD para indicar el inicio del procesamiento y la terminal XF1 se conecta a VCC para tener un estado conocido en esa entrada. La terminal IACK queda desconectada.

Todas las terminales del puerto serie (CLKR0, CLKX0, DR0, DX0, FSR0 y FSX0) y las de los temporizadores (TCLK0 y TCLK1) son conectadas a VCC para tener un estado conocido. Estos periféricos no son utilizados por la tarjeta. La terminal H1 se conecta a la terminal ADCLK del dispositivo PCI S5920 para servir como reloj del bus Add-On (ver funcionamiento del dispositivo S5920 más adelante). La terminal H3 se conecta al circuito divisor de frecuencia para generar la señal de reloj que se utiliza en la etapa de digitalización. Estas dos terminales, H1 y H3, proporcionan una señal de reloj de 20MHz. Las terminales X1 y X2/CLKIN están configuradas para trabajar con un cristal de 40MHz y generan la señal de reloj para el DSP.

Las terminales R/W, STRB y H1 se conectan a los CPLDs para ser utilizadas en la lógica de control. R/W indica si se desea hacer una lectura o una escritura por medio del bus primario. STRB es la señal que valida los datos en el bus primario, si esta señal esta habilitada, significa que los datos en el bus de datos y en el de direcciones son válidos. H1 es una señal de reloj de 20MHz con la que están sincronizadas las señales del bus primario.

Finalmente, las terminales EMU0-EMU2 se conectan a VCC para tener un estado conocido y la terminal EMU3 queda desconectada. Estas terminales no son utilizadas por la tarjeta.

#### 4.1.4 Interfaz PCI

Después de que el DSP ha terminado de procesar la señal y ha obtenido el espectro en frecuencia de la misma, los datos quedan almacenados en la memoria RAM de la tarjeta, listos para ser transferidos a la computadora. En este momento se hace uso del controlador PCI de la tarjeta, que nos ayuda a enviar los datos que se encuentran en la memoria RAM a un espacio en la memoria de la computadora, para ser utilizados por el software de aplicación.

El bus PCI fue definido por Intel para crear un estándar en la comunicación de dispositivos de una computadora [SA: 1995], [SW: 1998]. A continuación se mencionan algunas características del bus PCI, que muestran la importancia de esa interfaz en la actualidad, ya que es el estándar en las tarjetas de expansión para computadoras personales.

- Independiente del procesador. Los componentes diseñados para el bus PCI son específicos para PCI, no para el procesador, de esta manera, se aísla el diseño del dispositivo de los cambios en las actualizaciones de los procesadores.

- Soporte hasta para 256 dispositivos PCI funcionales por bus PCI. Aunque una implementación típica del bus PCI soporta aproximadamente 10 cargas eléctricas, cada paquete de dispositivo PCI puede contener hasta 8 funciones PCI diferentes. El bus PCI soporta lógicamente hasta 32 paquetes de dispositivo PCI físicos, para un total de 256 funciones PCI posibles por bus PCI.

- Soporte hasta para 256 buses PCI. La especificación proporciona soporte hasta para 256 buses PCI.

- Bajo consumo de poder. Una de las ventajas principales del diseño de la especificación PCI es la creación de un diseño del sistema que maneja tan poca corriente como es posible.

- Ráfagas utilizadas para todas las transferencias de escritura y lectura. Soporta una tasa de transferencia pico de 132 Mbytes por segundo para transferencias tanto de escritura como de lectura, una tasa de transferencia pico de 264 Mbytes por segundo para transferencias de 64 bits y una tasa de transferencia de hasta 528 Mbytes por segundo en un bus PCI de 66MHz.

- Velocidad del bus. La revisión 2.0 soporta una velocidad del bus de hasta 33MHz. La revisión 2.1 añade soporte para una operación del bus a 66MHz.

- Ancho de bus de 64 bits. Definición completa de una extensión para 64 bits.

- Acceso rápido. Tan rápido como 60ns.

- Soporte para maestro del bus. Un maestro PCI puede acceder a un objetivo que se encuentra en otro bus PCI abajo en la jerarquía del bus.

- Revisión de la integridad de la transacción. Revisión de la paridad en la dirección, comandos y datos.

- Tres espacios de direcciones. Espacio de direcciones para memoria, entrada/salida y configuración.

- Auto configuración. Especificación al nivel de bits de los registros de configuración necesarios para soportar la detección y configuración automática de periféricos.

- Tarjetas de expansión. La especificación incluye una definición de los conectores y de las tarjetas de expansión PCI, que pueden ser de tres tamaños.

Estas características hacen al bus PCI la arquitectura principal en el diseño de tarjetas de expansión para una computadora. Ver el Anexo B para una breve descripción de los ciclos de lectura y escritura del bus PCI.

#### 4.1.4.1 Operación del dispositivo PCI S5920

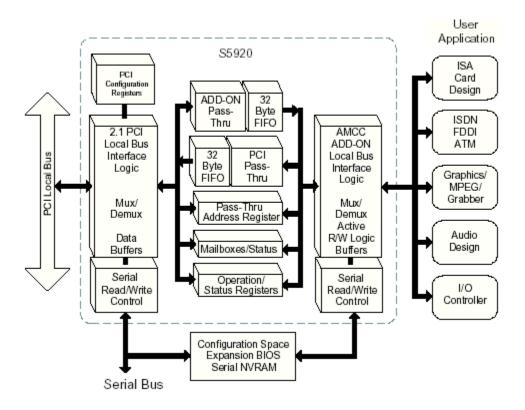

El dispositivo que permite a la tarjeta comunicarse con el bus PCI es el S5920 de la compañía AMCC. Este circuito integrado permite una tasa de transferencia de 132 Mbytes por segundo, ya que maneja el reloj a 33MHz y un bus de datos de 32 bits [AM: 1998]. También, transforma las señales del bus PCI en un bus llamado Add-On que es más fácil de utilizar y que permite realizar transferencias sencillas y de ráfaga. Este bus puede tener un ancho de datos de 8/16/32 bits. La figura 4.8 muestra el diagrama a bloques del dispositivo.

Este dispositivo se encuentra en la tarjeta PCI, lo que nos permite instalar la tarjeta en una ranura de expansión de una tarjeta madre de computadora que sea de tipo PCI. Este dispositivo también

nos permite enviar y recibir mensajes, con los cuales podemos manipular el funcionamiento del hardware de la tarjeta, para decirle que inicie la conversión, o que inicie el procesamiento o que se va a realizar una transferencia de datos entre la tarjeta y la computadora. En este último caso, la tarjeta envía los valores obtenidos después de realizar la FFT (espectro en frecuencia) a la computadora y ésta los requiere para graficar el espectro en la pantalla del monitor.

Figura 4.8. Diagrama a bloques del S5920.

El S5920 proporciona hasta 4 bloques de memoria o de entrada/salida a los cuales se les puede definir el tamaño, estos bloques son llamados regiones Pass-Thru. Las transferencias de datos a través de estas regiones pueden ser realizadas directamente al bus Add-On o por medio de dos FIFOs de 32 bytes.

Este controlador también cuenta con dos registros buzón de 32 bits para transferencias de datos adicionales o de comandos definidos por el usuario. Se puede examinar cada buzón para saber si está lleno o vacío, a un nivel de bytes, a través del registro de estado del buzón. El S5920 proporciona varios pines para los datos y para el control de los buzones que permiten realizar escrituras y lecturas directamente por hardware. Además, existe un pin dedicado para una interrupción del bus Add-On al bus PCI.

Finalmente, este circuito integrado da soporte para una memoria nvRAM (RAM no volátil) serial. Esto permite que el diseñador configure al dispositivo durante la inicialización, es decir, la nvRAM contiene los datos necesarios que se cargarán en los registros de configuración PCI. Esta memoria también puede servir como un BIOS de expansión.

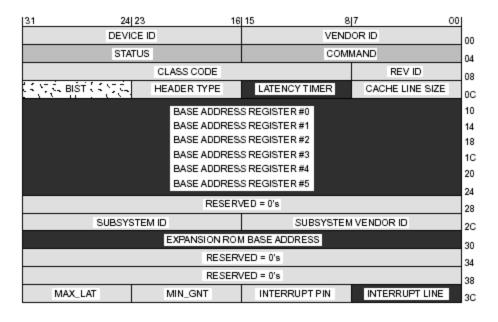

Todos los dispositivos PCI deben proporcionar un conjunto de registros llamados registros de configuración PCI. Éstos son leídos por el BIOS del sistema durante la inicialización y contienen información como fabricante, tipo de dispositivo, requerimientos de memoria y otros. Estos registros son cargados con valores por defecto o con los datos que se encuentran en la memoria serial.

Los accesos a las regiones Pass-Thru pueden ejecutar ciclos de bus PCI en tiempo real o a través de una FIFO interna. Las operaciones en tiempo real permiten al bus PCI escribir o leer directamente a los recursos del bus Add-On. El S5920 permite declarar hasta cuatro regiones Pass-Thru. Cada región puede ser definida como de 8, 16 ó 32 bits para espacio en memoria y de 32 bits para el espacio de entrada/salida. Cuando se requiere una escritura o una lectura del bus PCI, el dispositivo activa unos pines para señalarlo. La lógica de control del usuario decodifica estas señales para saber si es una lectura o una escritura, cuáles bytes están habilitados, qué región Pass-Thru es la indicada y si es un ciclo de acceso sencillo o de ráfaga. El canal Pass-Thru incorpora dos FIFOs de 32 bytes, una está dedicada para lecturas y otra para escrituras. Habilitando las FIFOs se pueden aceptar transferencias con ciclos de espera. El bus Add-On puede funcionar en dos modos: activo o pasivo. En el modo pasivo el usuario debe controlar los pines del circuito integrado para escribir o leer datos. En el modo activo, una máquina de estados interna controla al bus Add-On.

#### 4.1.4.2 Funcionamiento de la interfaz PCI de la tarjeta

La tarjeta está configurada para utilizar un ancho de bus de usuario de 32 bits. Se pueden realizar lecturas y escrituras con un ciclo de acceso de ráfaga a través de una región Pass-Thru, también se pueden enviar y recibir comandos hacia y desde la tarjeta por medio de un buzón. El bus Add-On queda configurado para ser utilizado en modo activo, dejando así que el S5920 controle las transferencias de datos en las regiones Pass-Thru.

Durante la inicialización, los registros de configuración PCI de la tarjeta se cargan con los valores que se encuentran en la memoria serial AT24C04 conectada a las terminales SCL y SDA del S5920. A continuación se describe la configuración, de los registros PCI (figura 4.9), que se requiere para que funcione adecuadamente el dispositivo en la tarjeta (los valores de todos los registros de configuración en la memoria serial se encuentran en el Anexo C):

- El registro de identificación del vendedor (VID) tiene un tamaño de 2 bytes. Este registro sirve para identificar al fabricante del dispositivo PCI, en este caso se carga con el valor 10E8h, que es el número que identifica a la compañía AMCC. Este número es asignado a cada compañía por el PCI Special Interest Group.

- El registro de identificación de dispositivo (DID) tiene un tamaño de 2 bytes. Asigna un número de referencia para el dispositivo, con este número se identifica al dispositivo dentro del sistema. El dispositivo utiliza el número de referencia 5920h.

- El registro de dirección base 0 (BADR0) tiene un tamaño de 4 bytes. Este registro se utiliza para tener acceso a los registros internos del S5920, como los buzones y los registros de estado. Este registro se carga con un valor de 10E8FF81h que define un espacio de entrada/salida de 128 bytes.

• El registro de dirección base 1 (BADR1) tiene un tamaño de 4 bytes. Este registro define la dirección de memoria base que se va a utilizar para acceder a la memoria de la tarjeta. Se carga con un valor de FFFFF01h, que define un espacio de entrada/salida de 256 bytes.

Figura 4.9. Registros de configuración PCI en el S5920.

A continuación se describe la configuración de las terminales (figura 4.10) necesarias para el funcionamiento adecuado del dispositivo S5920:

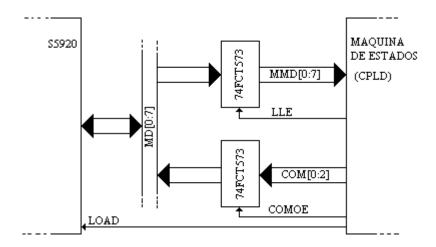

- La terminal MDMODE (modo de los datos del buzón) se conecta a GND para permitir que las terminales MD[7: 0] sean tanto de entrada como de salida.

- La terminal LOAD# se conecta a VCC por medio de un resistor para asegurar que las terminales MD[7: 0] siempre sean salidas, salvo cuando la lógica de control conduzca esta entrada a un nivel bajo para permitir la escritura de comandos en el buzón. Al conectar la terminal MDMODE a un estado bajo y a la terminal LOAD# a un estado alto, las terminales MD[7: 0] representan los datos del byte 3 del buzón de salida PCI, esto permite enviar comandos desde el bus PCI hacia el bus Add-On. Cuando la terminal LOAD# pasa a un estado bajo, las terminales MD[7: 0] representan los datos del byte 3 del buzón de entrada PCI, esto permite a la computadora recibir comandos desde el bus Add-On.

- La terminal PTMODE (modo del Pass-Thru) configura la operación del canal de datos Pass-Thru. Esta terminal se conecta a GND para que la región opere en modo activo, esto es, que el dispositivo controle las señales y los datos en el bus.

- La terminal PTRDY# se conecta a un estado alto para indicar que no se introducirán estados de espera externos en la transferencia de datos.

- La terminal DQMODE define el ancho del bus DQ cuando se opera en modo pasivo o cuando se desea escribir o leer los registros del dispositivo por el bus Add-On. En este caso no se realiza ninguna de las operaciones anteriores, pero se conecta la terminal a un estado bajo para que el ancho del bus sea de 32 bits.

- Las terminales ADR[6: 2] sirven para seleccionar a qué registro interno se desea tener acceso. En este caso no se realiza esta operación, pero se conectan estas terminales a un estado bajo.

- Las terminales BE[3: 0]# proporcionan la habilitación de bytes individuales en las operaciones de escritura y de lectura de registros. Estas terminales se conectan a un estado bajo para habilitar los cuatro bytes.

Figura 4.10. Terminales del dispositivo S5920.

- Las terminales SELECT#, WR# y RD# se utilizan para escribir o leer los registros desde el bus Add-On o para transacciones en el modo pasivo. La tarjeta no realiza las operaciones anteriores, por eso, las terminales se conectan a un estado alto, que inhabilita a estas señales.

- La terminal BPCLK queda desconectada y la terminal ADCLK se conecta a la terminal H1 del DSP para asegurar que el bus Add-On trabaje a una frecuencia de 20MHz.

- La terminal ADDINT# se conecta a un estado alto para asegurar que el bus Add-On no realizará una petición de interrupción al bus PCI. La terminal IRQ# queda desconectada.

- La terminal FLT# se conecta a un estado alto para asegurar que todas las terminales del dispositivo no serán flotadas.

- Las terminales DQ[31: 0] forman el bus de datos de 32 bits que se utiliza en las transferencias de datos por medio de la región Pass-Thru. Estas terminales se conectan a dispositivos

74FCT245 que controlan el bus de datos de la tarjeta, la señal PTWR controla la dirección de los datos en estos dispositivos.

- Las terminales PTBURST#, PTNUM[1: 0], PTBE[3: 0]# y PTADR# quedan desconectadas.

- Las terminales SYSRST#, PTATN#, PTWR y DXFR# se conectan a los CPLDs para ser utilizadas por la lógica de control.

- Las terminales MD[7: 0] son bidireccionales, por lo que se conectan a dos latches, uno de escritura y otro de lectura. Estos latches son controlados por una máquina de estados programada en un CPLD.

#### 4.2 Diseño de la lógica de control

Como dijimos en la sección 4.1, la lógica de control se encarga de administrar la secuencia de operaciones que debe realizar la tarjeta PCI. Tales operaciones pueden ser la inicialización del DSP o del ADC, la señalización de inicio de la conversión o del procesamiento, o que se va a realizar una transferencia por medio del bus PCI.

#### 4.2.1 Ecuaciones de control

En esta sección se describe la lógica de control implementada en dos CPLDs XC9536. En el primer CPLD se tienen las siguientes señales:

#### **Entradas**

- MMD0, MMD1, MMD2, MMD3, MMD4.

- DSPA16, DSPA17, DSPA18, DSPA19, DSPA20, DSPA21, DSPA22, DSPA23.

- STRB. RW.

- PTATN, PTWR, DXFR.

#### **Salidas**

- XF0, RESET, DSPOE, INT1.

- GDMR, WE

- COND1, COND2, COND3.

- ADCRES

- GDB12, GDB13, GDB14, GDB15.

- PCIOE.

Tabla 4.1. Comandos que envía la computadora a la tarjeta.

| Valor binario | Comando                                                         |  |

|---------------|-----------------------------------------------------------------|--|

| 00000         | No hay comando                                                  |  |

| 00011         | Transfiere programa desde la computadora a la RAM de la tarjeta |  |

| 00101         | Reset al DSP                                                    |  |

| 00110         | Habilita INT1                                                   |  |

| 01001 | Reset al ADC                                                 |  |

|-------|--------------------------------------------------------------|--|

| 01010 | Digitalizar señal de entrada                                 |  |

| 01100 | Transfiere datos desde la RAM de la tarjeta a la computadora |  |

| 10001 | Reset al generador de direcciones                            |  |

| 10010 | Procesar la señal en el DSP                                  |  |

Las señales MMD0-4 pertenecen a los 5 bits menos significativos del byte 3 del buzón de salida PCI (los tres bits restantes se usan para escoger una frecuencia de muestreo), que se utilizan para enviar mensajes de la computadora a la tarjeta, la tabla 4.1 muestra el significado de los comandos que pueden utilizarse.

Las señales DSPA(n), STRB y RW provienen del DSP (ver figura 4.7) y las señales PTATN, PTWR y DXFR provienen del circuito controlador del bus PCI (ver figura 4.10).

La señal XF0 se utiliza para indicarle al DSP que debe comenzar a procesar la señal digitalizada. Después de que el convertidor ha terminado de digitalizar la señal de entrada, la máquina de estados (implementada en el segundo CPLD) avisa a la computadora que es el momento de iniciar el procesamiento de la señal en el DSP. Mientras tanto el DSP está revisando de manera constante la terminal XF0 que le va a indicar el inicio del procesamiento. La terminal XF0 va a estar en un estado bajo si no hay procesamiento, y debe estar en estado alto durante el procesamiento. Ya que la computadora sabe que es el momento de procesar los datos, envía el comando correspondiente, en este caso 12h (ver tabla 4.1). A continuación se muestra la ecuación que describe la habilitación de la terminal XF0:

#### XF0 = MMD1 \* MMD4 \* /MMD2 \* /MMD0 \* /MMD3

La señal de RESET se utiliza para inicializar el DSP y además se utiliza en la secuencia del cargador de programa. Para cargar un programa en la memoria del DSP y que lo empiece a ejecutar, se requiere habilitar la señal de reset del DSP y posteriormente habilitar una de las interrupciones del DSP. Después de esto, el DSP comienza a leer una región de la memoria externa, donde debe encontrarse el programa a ser cargado. La señal de reset del DSP es activa en un nivel bajo, por lo que su ecuación resultante dado el comando 05h es:

#### /RESET = /MMD1 \* /MMD4 \* MMD2 \* MMD0 \* /MMD3

INT1 es la interrupción que se utiliza en la secuencia para cargar el programa de procesamiento en la memoria del DSP. Después de que se habilita la señal de reset, el DSP espera la habilitación de una señal de interrupción. Pueden ser cuatro las posibilidades de arranque, dependiendo qué número de interrupción se habilite. Con la INT1 se comienza a buscar el programa a partir de la dirección 40000h. Después de que se termina de cargar el programa, el DSP comienza a ejecutarlo automáticamente. INT1 es activa en bajo y el comando que envía la computadora es el 06h, entonces, su ecuación es:

#### /INT1 = MMD1 \* /MMD4 \* MMD2 \* /MMD0 \* /MMD3

DSPOE es la señal que controla los buses externos del C31, cuando está en estado bajo, el DSP tiene acceso a los datos y direcciones de la memoria RAM de la tarjeta, en estado alto, los buses

del DSP no pueden tener comunicación con la memoria de la tarjeta. Esta señal puede permitir al C31 el uso de la memoria RAM de la tarjeta cuando requiera un dato que se encuentre en el rango de 400000h a 40FFFFh. Este rango representa 64Kb de memoria RAM que tiene la tarjeta. Una dirección que se encuentre fuera de este rango no tendrá acceso a la memoria RAM. La señal STRB del DSP valida los datos en el bus de direcciones, la ecuación para DSPOE es:

```

/DSPOE = /STRB * /DSPA18 * /DSPA17 * /DSPA16 * DSPA22 * /DSPA23 * /DSPA20 * /DSPA21 * /DSPA19

```

La señal GDMR inicializa el generador de direcciones. Al inicio de una transferencia de datos entre la tarjeta y la computadora, o al inicio de la digitalización, el generador de direcciones TC74VHC4040 debe tener sus terminales en cero, esto se logra poniendo en estado alto su terminal MR, el comando de la computadora es 11h:

```

GDMR = /MMD1 * MMD4 * /MMD2 * MMD0 * /MMD3

```

WE es la señal que controla a la terminal del mismo nombre de las memorias. Esta terminal en estado bajo, indica una escritura en las memorias, en estado alto indica una lectura de las memorias. Esta terminal, normalmente va a estar en un estado bajo, es decir, de escritura, pero va a pasar a un estado alto cuando se cumpla cualquiera de las dos opciones siguientes. La primera, cuando el DSP desee leer la memoria RAM, en este caso su terminal STRB pasa a un estado bajo y su otra terminal RW queda en estado alto. La segunda, cuando el controlador PCI lea de las memorias, entonces sus terminales PTATN y PTWR pasan a estado bajo. Esta es la ecuación que controla la terminal WE:

```

WE = /STRB * RW + /PTATN * /PTWR

```

La señal COND1 es muy similar a la señal DSPOE, indica que se está direccionando una parte de la memoria RAM de la tarjeta. Cuando ocurre esto, COND1 pasa a un estado alto. Esta señal se ocupa en la lógica implementada en el segundo CPLD.

```

COND1 = /STRB * /DSPA18 * /DSPA17 * /DSPA16 * DSPA22 * /DSPA23 * /DSPA20 * /DSPA21 * /DSPA19

```